第一部分:半导体封装概念

半导体芯片封装是利用膜技术及细微加工技术,将芯片及其他元件在基板上布局、粘贴固定及连接,引出接线端子装配成完整的集成电路系统,并确保整个系统综合性能的工程。

第二部分:环境条件要求

杂质会对半导体的特性有着改变或破坏其性能的作用,所以在半导体器件生产过程中对一切杂质与生产环境都有着极其严格的控制要求,对杂质的控制涉及到多种类,如金属离子会破坏半导体器件的导电性能、尘埃粒子破坏半导体器件的表面结构等等。因此半导体封装工艺,必须要求在防静电条件良好的无尘车间内进行。其厂房洁净度要求根据不同的工艺环节从千级至十万级不等。

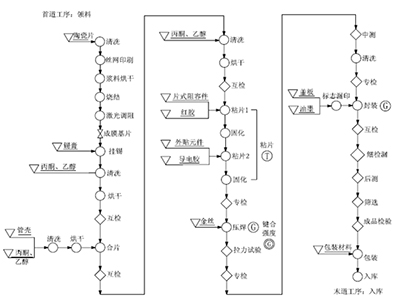

第三部分:封装工艺

3.1成膜基片制备

陶瓷基片是电子封装中绝缘特性、可靠性、机械强度、热膨胀系数、热导率、化学性能等关键参数中性能最为优异的基片形式。因而适用于航空航天、军事工程、通信设备、汽车电子、石油电子等对电子元器件质量性能要求较高的领域。

智腾混合集成电路的基片陶瓷,选用日本京瓷公司的陶瓷原料作为供应商的基体材料,选用美国杜邦公司的导体浆料(金浆料)和电阻浆料作为印料。通过高精度的全自动化丝网漏印工艺,利用美国BTU的温控烧结炉对成膜基片进行烧制。从而形成稳定可靠的以陶瓷为基材的无源网络,完成成膜基片的制备。

3.2成膜基片合片

成膜基片同电路外管壳的合片工艺,是决定载体电路同芯片外管壳机械连接强度的关键工艺环节。将焊料锡膏通过高精度全自动化丝网漏印工艺将锡膏均匀的印刷在成膜基片的底面,清洗烘干后,经过共晶焊炉,利用金锡共晶焊将成膜基片同电路外观可焊接成为一体。金锡合金的屈服强度很高,即使在250~260℃的温度下,它的强度也能够胜任气密性的要求,保障电路后续在复杂工况下的长期稳定工作。

3.3全自动裸片贴装

裸片(DIE)的贴装过程被成为DIE BOND贴片技术,利用全自动DIE BOND设备,将裸片(DIE)和贴片阻容器件按照设计好的贴装图纸贴装在合片后的无源网络中。根据工况环境对集成电路内部贴装温度、应力大小、贴装强度等技术条件的不同要求,通常智腾会主要采用共晶焊接法、树脂粘合法和焊锡结合法三种工艺方式来实现。

3.4邦定键合

Wire Bonding (压焊,也称为绑定,键合,丝焊)工艺,智腾是通过美国KNS的全自动键合设备,实现最小35um线间距,±2.5um@Sigma焊点精度的精度水平,完成单条导线的焊线时间小于23毫秒。使用金属丝(金线、铝线等),利用热超声能源,完成集成电路内部微电子器件及外管壳间互连接线的连接,即芯片与电路或引线框架之间的连接。

3.5氮气封装

封装(Package)对于集成电路而言是至关重要的一个公益环节。它不只起着维护内部芯片和加强导热性能等的作用,还是沟通集成电路内部世界与外部电路系统的桥梁。智腾的高等级集成电路,通常采用平行缝焊和激光焊的工艺,在99.99%\99.999%的高纯氮气环境下对集成电路进行气密性封装。在封装后,利用真空检漏仪、瑞士英福康的氦质谱检漏仪、PIND颗粒碰撞噪声检测仪等设备对密封效果及密封洁净度进行检测。金属或陶瓷气密性封装的可靠性远高于普通的塑封封装,因此非常适用于于航空航天、国防科技、通信工程、汽车电子、石油电子等领域。

3.6成品检验

封装完毕的集成电路会根据使用环境的要求,借鉴GJB2438B-2017的国军标标准,经过电气功能测试、高温老化测试、高低温循环测试、耐盐雾测试、湿热测试、高温振动测试、冲击测试等相关试验内容完成成品检测,而后入库,提供给用户。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。